Embedded SoPC Design with Nios II Processor and VHDL Examples: Chu, Pong P.: 9781118008881: Amazon.com: Books

How we developed the NIOS II processor module for IDA Pro - Malware Analysis - Malware Analysis, News and Indicators

Novel architecture for hardware efficient FPGA implementation of real time configurable “variable point FFT” using NIOS II™ | Semantic Scholar

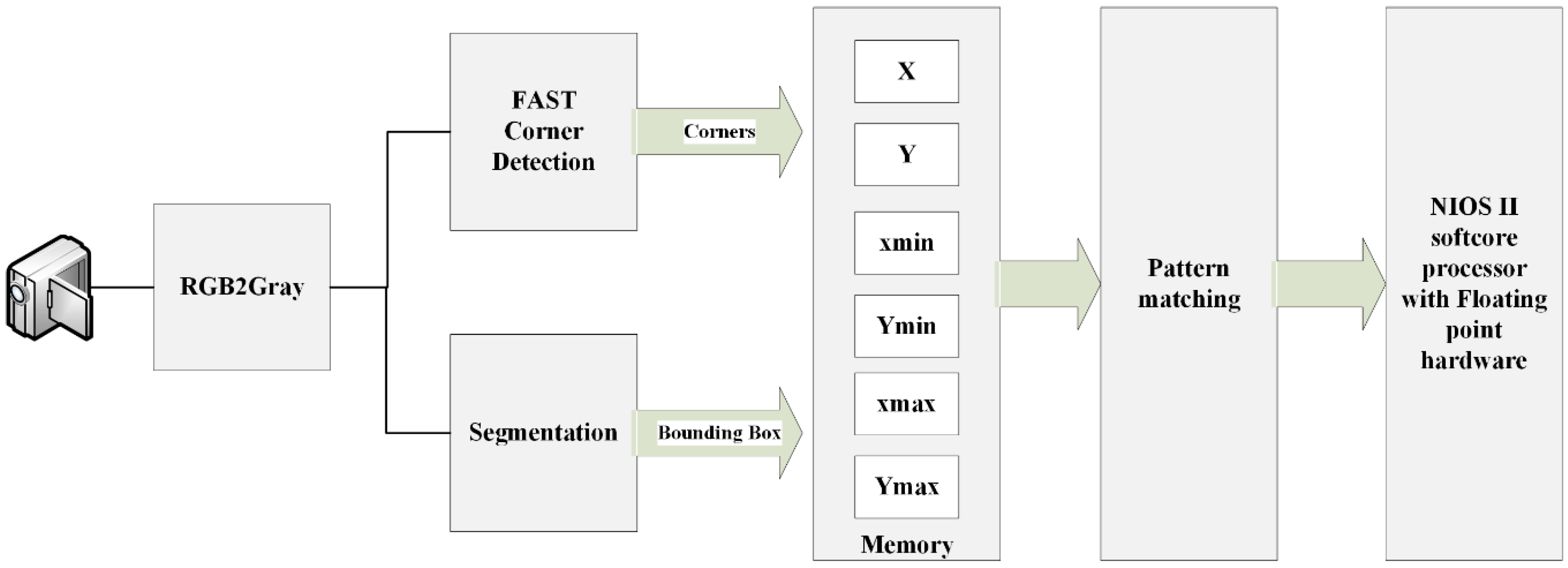

Sensors | Free Full-Text | A Real-Time Marker-Based Visual Sensor Based on a FPGA and a Soft Core Processor

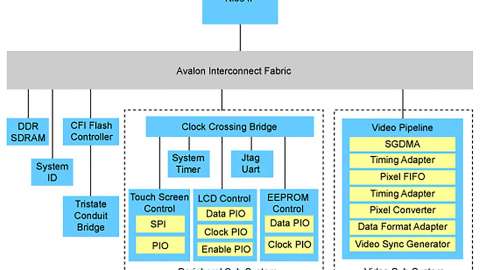

Electronics | Free Full-Text | XML-Based Automatic NIOS II Multi-Processor System Generation for Intel FPGAs

![2: Nios II CPU architecture [4] | Download Scientific Diagram 2: Nios II CPU architecture [4] | Download Scientific Diagram](https://www.researchgate.net/publication/220841654/figure/fig4/AS:305566615392268@1449864166489/Nios-II-CPU-architecture-4.png)